集成電路設計實戰 從Tanner Tools入門到精通

在當今信息技術飛速發展的時代,集成電路(IC)設計已成為電子工程領域的核心。Tanner Tools作為一款功能全面、易于上手的EDA(電子設計自動化)軟件套件,為眾多工程師、研究人員和學生提供了從概念到物理實現的完整設計流程。本文將深入探討如何利用Tanner Tools進行集成電路設計實戰,涵蓋關鍵步驟、工具應用與設計技巧。

一、 設計起點:架構規劃與原理圖輸入

任何成功的IC設計都始于清晰的需求分析與架構規劃。在Tanner環境中,這一階段通常使用S-Edit進行。設計師首先需要明確電路的功能、性能指標(如速度、功耗、面積)以及工藝節點。接著,在S-Edit中創建頂層模塊,通過繪制原理圖來定義各子模塊(如運算放大器、數字邏輯門、存儲器單元等)之間的互連關系。此時,建立清晰、分層的模塊化設計至關重要,它能極大提升后續仿真和版圖設計的效率與可維護性。

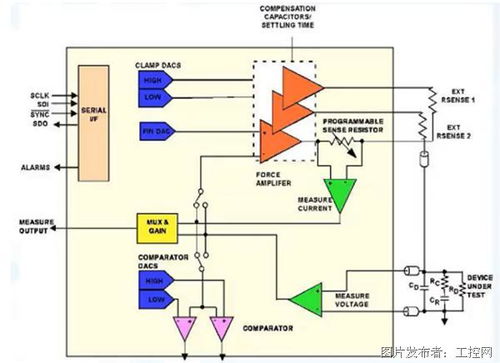

二、 電路仿真驗證:性能預測與優化

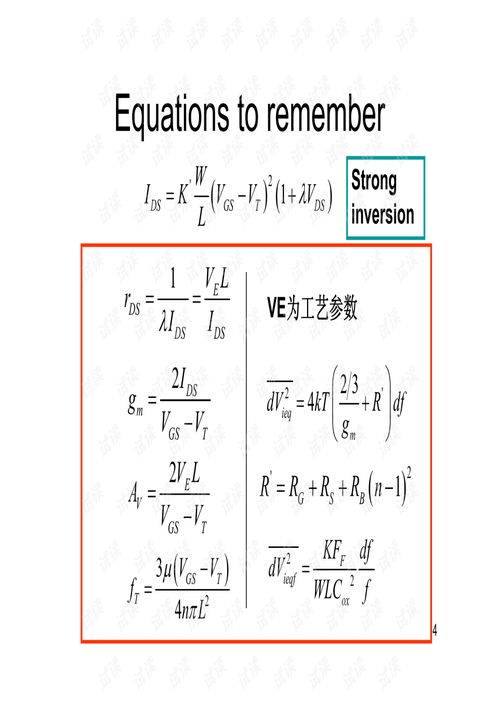

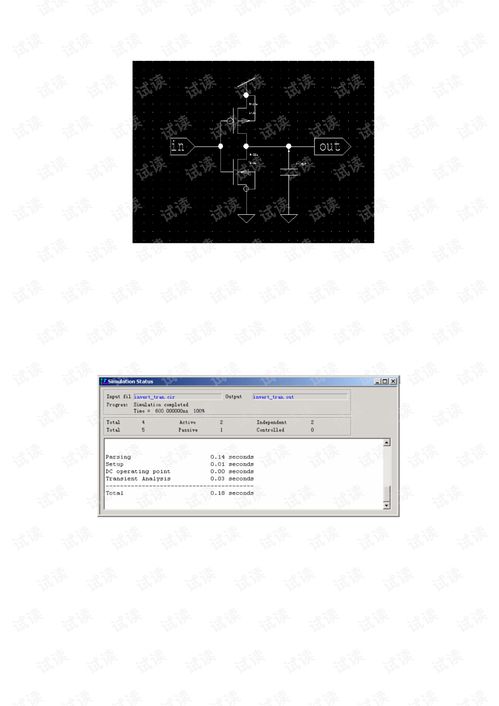

完成原理圖設計后,必須通過仿真來驗證電路功能與性能是否達標。Tanner T-Spice是執行這一任務的強大工具。設計師需要為電路元件(晶體管、電阻、電容等)加載準確的工藝模型文件(通常由晶圓廠提供)。通過T-Spice,可以進行:

1. 瞬態分析:觀察電路在時域下的響應,如數字信號的翻轉、模擬信號的建立時間。

2. 直流分析:確定電路的靜態工作點、傳輸特性曲線(如放大器的增益)。

3. 交流分析:分析電路的頻率響應、帶寬、相位裕度等。

仿真是迭代優化的核心環節。根據仿真結果,設計師需要反復調整晶體管尺寸、偏置條件或電路拓撲,直至滿足所有規格。

三、 物理實現:版圖設計與驗證

當電路在仿真中表現優異后,便進入物理實現階段——版圖設計。這是將電路原理圖轉化為可用于芯片制造的幾何圖形(多邊形)的過程。Tanner L-Edit是業界廣泛使用的版圖編輯器。

- 版圖繪制:遵循嚴格的設計規則(DRC),在特定的工藝層上繪制晶體管、接觸孔、互連線等。版圖設計需綜合考慮性能(如減小寄生電阻電容)、面積利用率和可制造性。

- 版圖與原理圖對照(LVS):使用L-Edit內嵌的驗證工具,確保繪制的版圖與原始電路原理圖在電氣連接上完全一致。這是避免制造錯誤的關鍵一步。

- 寄生參數提取與后仿真:從完成的版圖中提取寄生電阻和電容,并將其反標回T-Spice中進行后仿真。這一步至關重要,因為版圖引入的寄生效應可能顯著影響電路的實際性能(如降低速度、增加功耗)。只有后仿真結果合格,設計才算真正完成。

四、 實戰技巧與高級應用

- 混合信號設計:Tanner工具鏈能很好地支持模擬與數字混合信號設計。設計師可以在同一環境中處理模擬模塊和數字標準單元,并進行整體仿真。

- 版圖自動化:對于重復性結構(如存儲器陣列、電容陣列),可以利用L-Edit的“實例化”和“陣列”功能提高繪制效率,或編寫腳本實現部分自動化。

- 設計復用與IP管理:建立并維護經過驗證的單元庫(標準單元、模擬單元),在新項目中復用,能大幅縮短設計周期。

五、

通過Tanner Tools進行集成電路設計,是一個從抽象到具體、不斷迭代驗證的工程過程。從S-Edit的原理圖構思,到T-Spice的仿真優化,再到L-Edit的版圖實現與驗證,每一步都緊密相連,要求設計師兼具電路理論知識和工程實踐技能。熟練掌握這套流程,不僅能完成從簡單模塊到復雜系統的設計,更能深刻理解集成電路從“想法”到“硅片”的完整生命周期。對于初學者而言,從一個小型項目(如一個反相器或一個兩級運放)開始,完整地走通整個流程,是邁入IC設計殿堂最有效的實戰路徑。

如若轉載,請注明出處:http://m.xiangyujixie.cn/product/74.html

更新時間:2026-04-16 10:37:37